# MIR Patterns for GloballSel Combiners

Pierre van Houtryve

# GloballSel

- DAGISel alternative

- Uses (g)MIR

- Function scope

```

name: sbfx_s32_vii

body: |

bb.0:

liveins: $vgpr0

%0:vgpr(s32) = COPY $vgpr0

%1:vgpr(s32) = G_CONSTANT i32 2

%2:vgpr(s32) = G_CONSTANT i32 10

%3:vgpr(s32) = G_SBFX %0, %1(s32), %

S_ENDPGM 0, implicit %3

```

%0.vgpr\_32 = corr \$vgpro

%1:vgpr\_32 = V\_MOV\_B32\_e32 2, implicit \$exec

%2:vgpr\_32 = V\_MOV\_B32\_e32 10, implicit \$exec

%3:vgpr\_32 = V\_BFE\_I32\_e64 %0, %1, %2, implicit \$exec

S\_ENDPGM 0, implicit %3

#### **GloballSel Combiners**

- Matches and rewrites code patterns

- Generic rules & target-specific rules

| name:               | mul_by_zero               |

|---------------------|---------------------------|

| body:               |                           |

| bb.0:               |                           |

| liveins:            | \$×0                      |

|                     |                           |

| %0:_(s64            | ) = COPY \$×0             |

| %1:_(s64            | ) = G_CONSTANT i64 0      |

| %2:_(s64            | $) = G_MUL \%0, \%1(s64)$ |

| \$x0 = COPY %2(s64) |                           |

#### **GloballSel Combiners: Input Before**

// Fold (fabs (fneg x)) -> (fabs x).

def fabs\_fneg\_fold: GICombineRule <

(defs root:\$root, build\_fn\_matchinfo:\$matchinfo),

(match (wip\_match\_opcode G\_FABS):\$root,

[{ return Helper.matchCombineFAbsOfFNeg(\*\${root}, \${matchinfo}); }]),

(apply [{ Helper.applyBuildFnNoErase(\*\${root}, \${matchinfo}); }])>;

#### **GloballSel Combiners: Input Before**

# **GloballSel Combiners: Output Before**

```

if (Partition == 4 /* TargetOpcode::G FREEZE */) {

// Leaf name: idempotent_prop

// Rule: idempotent_prop

if (!RuleConfig->isRuleDisabled(4)) {

if (1

<u>&&</u> [<u>&</u>]() {

return MRI.getVRegDef(MIs[0]->getOperand(1).getReg())->getOpcode() == MIs[0]->getOpcode();

return true;

}()

) {

LLVM_DEBUG(dbgs() << "Applying rule 'idempotent_prop'\n");</pre>

Helper.replaceSingleDefInstWithOperand(*MIs[0], 1);

return true;

}

return false;

}

```

# **GloballSel Combiners: Refactoring Goals**

- Unify InstructionSelector and combiners infrastructure

- Allow doing more in pure TableGen (e.g., rewriting patterns)

#### **GloballSel Combiners: Input After**

```

// Fold (fabs (fneg x)) -> (fabs x).

def fabs_fneg_fold: GICombineRule <

(defs root:$dst),

(match (G_FNEG $tmp, $x),

(G_FABS $dst, $tmp)),

(apply (G_FABS $dst, $x))>

```

# **GloballSel Combiners: Input After**

(apply (GIReplaceReg \$dst, \$src))>;

```

AMD

together we advance_

```

#### **GloballSel Combiners: Type Inference**

```

// Rule Operand Type Equivalence Classes for inference_mul_by_neg_one:

Groups for ___inference_mul_by_neg_one_match_0:

[dst, x]

11

Groups for __inference_mul_by_neg_one_apply_0:

[dst, x]

11

Final Type Equivalence Classes: [dst, x]

11

INFER: imm 0 -> GITypeOf<$x>

11

def inference_mul_by_neg_one: GICombineRule <</pre>

(defs root:$dst),

(match (G_MUL $dst, $x -1)),

(apply (G_SUB $dst, 0, $x))

>

```

# **GloballSel Combiners: Output After**

GIM\_Try, /\*On fail goto\*//\*Label 289\*/ GIMT\_Encode4(4579), // Rule ID 5 // GIM\_CheckSimplePredicate, GIMT\_Encode2(GICXXPred\_Simple\_IsRule4Enabled), // MIs[0] dst // No operand predicates // MIs[0] src GIM RecordInsnIgnoreCopies, /\*DefineMI\*/1, /\*MI\*/0, /\*OpIdx\*/1, // MIs[1] GIM\_CheckOpcode, /\*MI\*/1, GIMT\_Encode2(TargetOpcode::G\_FABS), // MIs[1] \_\_idempotent\_prop\_match\_0.x // No operand predicates GIM\_CheckCanReplaceReg, /\*OldInsnID\*/0, /\*OldOpIdx\*/0, /\*NewInsnId\*/0, /\*NewOpIdx\*/1, GIM CheckIsSafeToFold, /\*InsnID\*/1, // Combiner Rule #4: idempotent\_prop @ [\_\_\_idempotent\_prop\_match\_0[1]] GIR ReplaceReg, /\*OldInsnID\*/0, /\*OldOpIdx\*/0, /\*NewInsnId\*/0, /\*NewOpIdx\*/1, GIR\_EraseFromParent, /\*InsnID\*/0, **GIR** Done

# **GloballSel Combiners: Error Handling**

- "Assert is an error" -> Diagnose errors, assert is a bug

- Every diagnostic is tested

error: invalid output operand 'x': operand is not a live-in of the match pattern, and it has no definition

error: pattern 'foo' ('COPY') is unreachable from the pattern root!

```

warning: impossible type constraints: operand 1 of 'broken' has type 'i64', but 'TypedParams' constrains it

to 'i32'

note: operand 1 of 'broken' is 'k'

note: argument 1 of 'TypedParams' is 'i'

```

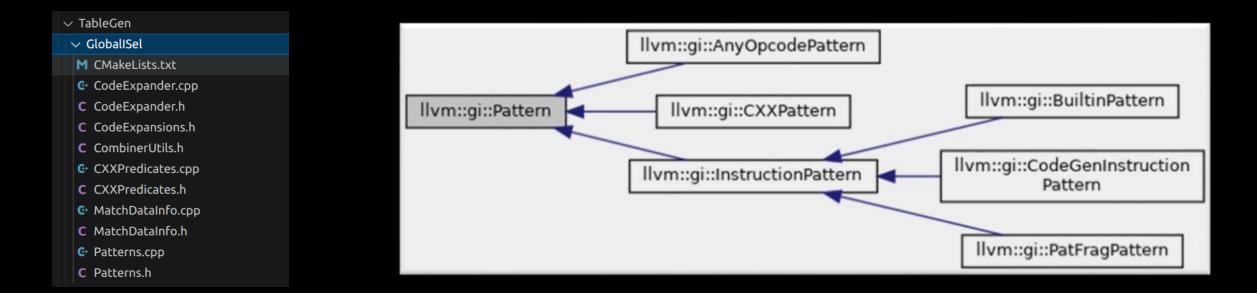

# **GloballSel Combiners: Backend Design**

- Good test coverage!

- Designed with reusability in mind (to some extent)

# **GloballSel Combiners: Limitations**

- MIR patterns are (currently) only for simple patterns

- Many rules still need a blend of C++ and MIR patterns, or full C++

- MIR patterns cannot...

- Use KnownBits

- Constraint constants (e.g., K is a multiple of 2)

- Express constraints on types other than equality (e.g., T is 32 bits or lower)

- Recursively match something

- o Etc.

# **GloballSel MIR Patterns: What Now?**

- Patterns become increasingly difficult to port

- Effort >>> Reward

- Feel free to request features by opening an issue

- Should we try using MIR patterns for ISel?

- Interested? Come talk!

- DAG Syntax can be limiting

- Should we consider parsing MIR directly at some point?

# Do you like the concept of MIR patterns and have ideas? Let's discuss!

# **Copyright and disclaimer**

©2024 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions, and typographical errors. The information contained herein is subject to change and may be rendered inaccurate releases, for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. Any computer system has risks of security vulnerabilities that cannot be completely prevented or mitigated. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

▶ THIS INFORMATION IS PROVIDED 'AS IS." AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS, OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION. AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY RELIANCE, DIRECT, INDIRECT, SPECIAL, OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION

#