# AN INTERNAL REPRESENTATION FOR ADAPTIVE ONLINE PARALLELIZATION

by

Koy D. Rehme

A thesis submitted to the faculty of

Brigham Young University

in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering

Brigham Young University

August 2009

Copyright  $\bigodot$  2009 Koy D. Rehme

All Rights Reserved

## BRIGHAM YOUNG UNIVERSITY

## GRADUATE COMMITTEE APPROVAL

of a thesis submitted by

Koy D. Rehme

This thesis has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

Date

David A. Penry, Chair

Date

Michael J. Wirthlin

Date

James K. Archibald

### BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the thesis of Koy D. Rehme in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

Date

David A. Penry Chair, Graduate Committee

Accepted for the Department

Michael J. Wirthlin Graduate Coordinator

Accepted for the College

Alan R. Parkinson Dean, Ira A. Fulton College of Engineering and Technology

#### ABSTRACT

## AN INTERNAL REPRESENTATION FOR ADAPTIVE ONLINE PARALLELIZATION

Koy D. Rehme

Department of Electrical and Computer Engineering

Master of Science

Future computer processors may have tens or hundreds of cores, increasing the need for efficient parallel programming models. The nature of multicore processors will present applications with the challenge of diversity: a variety of operating environments, architectures, and data will be available and the compiler will have no foreknowledge of the environment until run time. Adaptive Online Parallelization (ADOPAR) is a unifying framework that attempts to overcome diversity by separating discovery and packaging of parallelism. Scheduling for execution may then occur at run time when diversity may best be resolved.

This work presents a compact representation of parallelism based on the task graph programming model, tailored especially for ADOPAR and for regular and irregular parallel computations. Task graphs can be unmanageably large for fine-grained parallelism. Rather than representing each task individually, similar tasks are grouped into *task descriptors*. From these, a *task descriptor graph*, with *relationship descriptors* forming the edges of the graph, may be represented. While even highly irregular

computations often have structure, previous representations have chosen to restrict what can be easily represented, thus limiting full exploitation by the back end. Therefore, in this work, task and relationship descriptors have been endowed with *instantiation functions* (methods of descriptors that act as factories) so the front end may have a full range of expression when describing the task graph. The representation uses descriptors to express a full range of regular and irregular computations in a very flexible and compact manner.

The representation also allows for dynamic optimization and transformation, which assists ADOPAR in its goal of overcoming various forms of diversity. We have successfully implemented this representation using new compiler intrinsics, allow ADOPAR schedulers to operate on the described task graph for parallel execution, and demonstrate the low code size overhead and the necessity for native schedulers.

#### ACKNOWLEDGMENTS

Any work of sufficient size requires the help of many people. This thesis is no different. Many hours have been spent researching, programming, and writing, with each hour supported by someone else. My thanks go to all friends, family, and coworkers for their assistance in getting this thesis done. My name may go under the title, but each of theirs deserves to be there as well.

I transferred to BYU without knowing what the future would hold for me. Without prior contacts with professors, I needed some way of starting up my research. Dr. Penry, being a new professor here, made for a perfect match: he needed students for his research, I needed a advisor for mine. I have expanded my knowledge under his guidance, and I hope this thesis shows that.

I wondered if I would ever finish this thesis, especially after each of my four computer failures. I am very thankful for backups ... and for the loaner from Dawn and Gary Goldwasser that got me through to the end.

And most of all I want to thank my wife Becky. She made sure there was always a carrot to motivate me and didn't spare the whip when gentle reminders failed. She even served as an editor, receiving but a peanut in return. Without her encouragement I would still be working on the first chapter.

## Table of Contents

| A                 | Acknowledgements |                                |     |

|-------------------|------------------|--------------------------------|-----|

| Li                | st of            | Tables                         | xix |

| List of Figures x |                  |                                | xii |

| 1 Introduction    |                  |                                | 1   |

|                   | 1.1              | Motivation                     | 3   |

|                   |                  | 1.1.1 The Manycore Era         | 3   |

|                   |                  | 1.1.2 Discovery of Parallelism | 4   |

|                   |                  | 1.1.3 Packaging of Parallelism | 5   |

|                   |                  | 1.1.4 The Run-time Advantage   | 6   |

|                   | 1.2              | The ADOPAR Vision              | 6   |

|                   | 1.3              | Parallelism Representation     | 8   |

|                   | 1.4              | Contributions and Objectives   | 9   |

|                   | 1.5              | Outline                        | 11  |

| <b>2</b>          | Bac              | kground and Related Work       | 13  |

|                   | 2.1              | Scheduling and Execution       | 13  |

|                   | 2.2              | Parallel Programming Paradigms | 15  |

|                   |                  | 2.2.1 Types of Parallelism     | 16  |

|                   | 2.3              | Data-Parallel Representations  | 17  |

|   | 2.4 | Loop-  | Parallel Representations          | 20 |

|---|-----|--------|-----------------------------------|----|

|   | 2.5 | Task-I | Parallel Representations          | 21 |

|   | 2.6 | Summ   | ary                               | 23 |

| 3 | The | e ADO  | PAR Representation                | 25 |

|   | 3.1 | Fine-C | Grained Task Model                | 27 |

|   | 3.2 | Static | Task Graph                        | 28 |

|   |     | 3.2.1  | Task Types                        | 30 |

|   |     | 3.2.2  | Synchronization Primitives        | 31 |

|   | 3.3 | The A  | DOPAR Internal Representation     | 32 |

|   |     | 3.3.1  | Task and Relationship Descriptors | 33 |

|   |     | 3.3.2  | IR Creation Process               | 36 |

|   | 3.4 | Exam   | ples                              | 36 |

|   |     | 3.4.1  | Linear Algebra                    | 37 |

|   |     | 3.4.2  | Iterative Linear System Solvers   | 42 |

|   | 3.5 | Future | e Transformations on the TDG      | 46 |

|   |     | 3.5.1  | Inlining and Extraction           | 48 |

|   |     | 3.5.2  | Descriptor Splitting              | 48 |

|   |     | 3.5.3  | Flattening                        | 49 |

|   | 3.6 | Granu  | larity Adjustments                | 50 |

|   |     | 3.6.1  | Discrete Task Combining           | 51 |

|   |     | 3.6.2  | Task Descriptor Combining         | 52 |

|   |     | 3.6.3  | Hierarchy Combining               | 53 |

|   | 3.7 | Summ   | ary                               | 53 |

| 4 | Imr | olemen | tation                            | 55 |

| - | 4.1 |        | onment                            | 55 |

|   |     | / •• • |                                   |    |

|          |     | 4.1.1 LLVM                              |

|----------|-----|-----------------------------------------|

|          |     | 4.1.2 Scheduler                         |

|          | 4.2 | ADOPAR Intrinsics                       |

|          |     | 4.2.1 Parameters and Types              |

|          |     | 4.2.2 TDG Creation Intrinsics           |

|          |     | 4.2.3 Instantiation Function Intrinsics |

|          |     | 4.2.4 Querying and Execution Intrinsics |

|          | 4.3 | TDG Creation                            |

|          | 4.4 | Code Transformations                    |

|          | 4.5 | Examples                                |

|          |     | 4.5.1 Sparse Linear Systems             |

|          | 4.6 | Summary                                 |

| <b>5</b> | Eva | luation 79                              |

|          | 5.1 | Methodology                             |

|          |     | 5.1.1 Criteria                          |

|          |     | 5.1.2 Metrics                           |

|          |     | 5.1.3 Benchmarks                        |

|          | 5.2 | Measurements                            |

|          |     | 5.2.1 Code Size Overhead                |

|          |     | 5.2.2 Compilation Time Overhead         |

|          |     | 5.2.3 Task Instantiation Overhead       |

|          |     | 5.2.4 Scheduling Results                |

|          | 5.3 | Summary                                 |

| 6        | Cor | clusion 91                              |

|          | 6.1 | Summary of Results                      |

|          |     |                                         |

| 6.2          | Future | Work                      | 91 |  |

|--------------|--------|---------------------------|----|--|

|              | 6.2.1  | Representation            | 92 |  |

|              | 6.2.2  | Front Ends                | 94 |  |

|              | 6.2.3  | Analysis and Optimization | 95 |  |

| 6.3          | Summa  | ary                       | 96 |  |

| 6.4          | A Fine | l Word                    | 96 |  |

|              | ,      |                           | 97 |  |

| Bibliography |        |                           |    |  |

## List of Tables

| 4.1 | Relationship Values               | 59 |

|-----|-----------------------------------|----|

| 4.2 | Task Creation Intrinsics          | 61 |

| 4.3 | Instantiation Intrinsics          | 64 |

| 4.4 | Querying and Execution Intrinsics | 66 |

# List of Figures

| 3.1  | Task Descriptors                                      | 29 |

|------|-------------------------------------------------------|----|

| 3.2  | Hierarchical Tasks                                    | 29 |

| 3.3  | Barrier Implementation                                | 32 |

| 3.4  | Pseudocode: Dense Matrix-Vector Multiply              | 37 |

| 3.5  | Dense Matrix-Vector Multiply TDG                      | 38 |

| 3.6  | Matrix-Vector TIG (Exclusive)                         | 38 |

| 3.7  | Dense Matrix-Vector Multiply TDG (Summing Tree)       | 39 |

| 3.8  | Matrix-Vector TIG (Summing Tree)                      | 40 |

| 3.9  | Dense Matrix-Vector Multiply TDG (Blocked)            | 41 |

| 3.10 | Matrix-Vector TIG (Blocked)                           | 41 |

| 3.11 | Dense Matrix-Vector Multiply TDG (Granularity Change) | 41 |

| 3.12 | Matrix-Vector TIG (Granularity Change)                | 42 |

| 3.13 | Pseudocode: Dense Jacobi Linear Solver                | 43 |

| 3.14 | Jacobi LU TDG                                         | 44 |

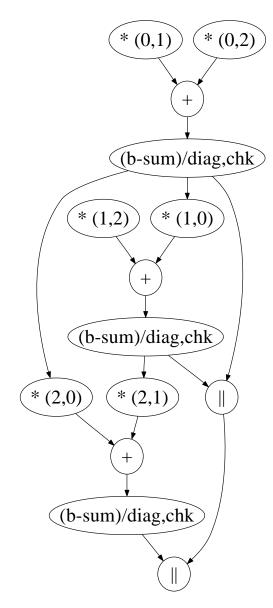

| 3.15 | Jacobi LU TIG                                         | 45 |

| 3.16 | Pseudocode: Dense Gauss-Seidel Linear Solver          | 45 |

| 3.17 | Gauss Seidel LU TDG                                   | 46 |

| 3.18 | Gauss-Seidel LU TIG                                   | 47 |

| 3.19 | Flattening the Hierarchy                              | 50 |

| 4.1  | Root Task Creation                                    | 62 |

| 4.2  | Example Serial Algorithm                                                  | 67 |

|------|---------------------------------------------------------------------------|----|

| 4.3  | Task Body                                                                 | 67 |

| 4.4  | Instantiation Functions                                                   | 68 |

| 4.5  | Example TDG                                                               | 69 |

| 4.6  | Annotated Jacobi Linear System Algorithm                                  | 72 |

| 4.7  | Sparse Linear System Task Hierarchy                                       | 73 |

| 4.8  | Sparse Linear System Instantiation Functions                              | 74 |

| 4.9  | Sparse Linear System Task Bodies                                          | 75 |

| 4.10 | Sparse Linear System Relationship Instantiation Functions $\ldots \ldots$ | 77 |

| 4.11 | Gauss-Seidel Modification                                                 | 78 |

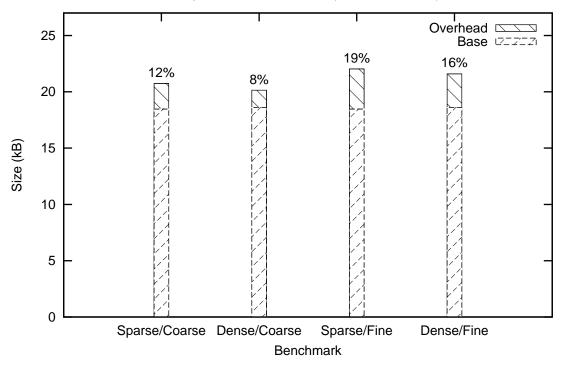

| 5.1  | Code Size Overhead                                                        | 83 |

| 5.2  | Compilation Time Overhead                                                 | 84 |

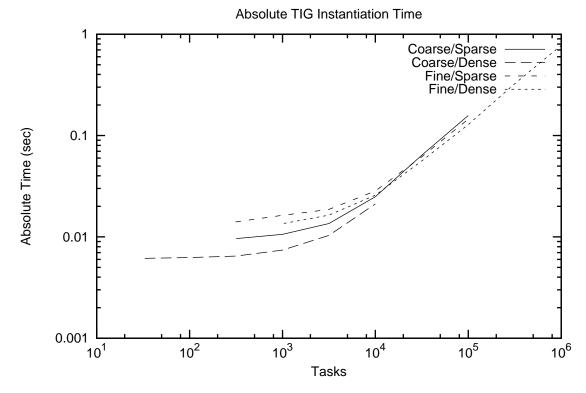

| 5.3  | Absolute Instantiation Overhead                                           | 86 |

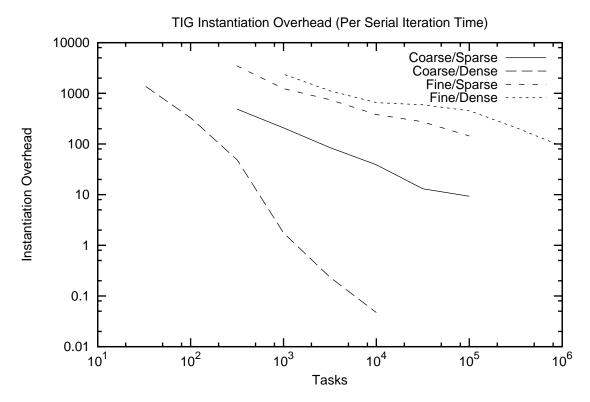

| 5.4  | Relative Instantiation Time                                               | 87 |

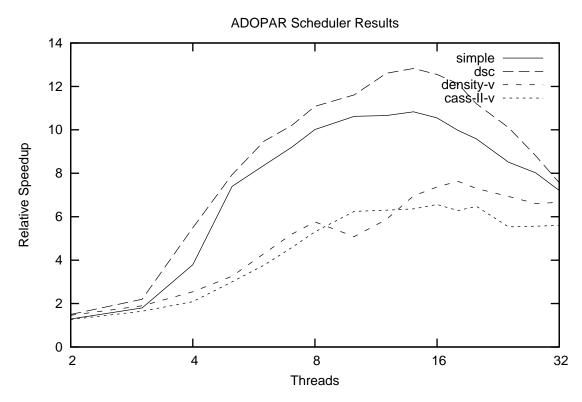

| 5.5  | ADOPAR Scheduler Results                                                  | 89 |

## Chapter 1

### Introduction

Advances in the fields of processor architecture, compiler research, and process development have contributed to exponential performance improvements of the microprocessor. The resulting performance improvements strive to satisfy the evergrowing processing requirements of consumers, industry, and researchers. Although one cannot reasonably expect advances to continue indefinitely, we have yet to see the end of Moore's Law [1]. Transistor manufacturing improvements will continue to provide more raw processing capabilities in the future.

Both research and commercial products have transitioned from using additional transistors to improve performance of a single processor to a "step and repeat" replication of many processors on a single die. These Chip Multi-Processors (CMPs) [2] give a significant potential improvement for software. Unfortunately, software cannot necessarily take advantage of the extra processing power without being rewritten or at least recompiled. Even then, new techniques need to be developed to utilize all cores to full potential.

Irregular computations, such as those found in sparse linear algebra and molecular dynamics, are especially difficult for software. The irregularity of these computations impede the static compiler analyses normally used to optimize parallelization; however, optimizations are possible once the dynamic nature of the system is resolved and communication patterns are determined. Current compiler research is developing dynamic frameworks which can optimize at run time as long as the parallelism is represented appropriately.

Compilers and optimizers rely on an Internal Representation (IR), or the specific method for representing the structure of a program. The representation determines how optimizations and analyses are performed and impacts the performance of the compiler and final executable. Many IRs are possible, depending on the goal of the system: Chapter 2 describes several that are currently used. The *task graph* representation for parallelism provides a mechanism for describing irregular parallel computations and communications. As the task size decreases and the number of tasks increases, more parallelism can be found in the graph; however, smaller task sizes also dramatically increase the amount of computation needed to operate on the graph and increase the final run-time overhead (given the larger number of tasks). While algorithm researchers are trying to reduce the complexity of scheduling algorithms, it is not uncommon to see algorithms from  $O(n \log n)$  in the best case to  $O(2^n)$  and worse.

Working within a dynamic environment may relieve the difficulties of creating parallel code while providing specialized optimization opportunities for the application. Dynamic optimization of serial programs may use information only available during execution; the hope is that parallel programs may receive the same benefit. Since the operating environment may only be known when executing the program, these same optimizations may be specialized for the immediate situation. As such it is important to include as much information as possible into the parallelism representation so it can be accessed at run time.

This work presents two modifications of the task graph representation specific to a dynamic environment. The first is the addition of highly generic *task descriptors*, a conceptual "factory" for tasks. Task relationships are formed with *relationship descriptors*, which form the edges of the task graph. The second modification is the concept of *instantiation functions*, where control of task and relationship descriptors is governed by a section of code which describes the tasks procedurally. Instantiation functions provide flexibility to represent irregular computations with arbitrary patterns while also providing a mechanism to reduce the complexity of compiler analysis and scheduling. Embedding the algorithmic descriptions of tasks and relationships into instantiation functions can improve performance by increasing the effectiveness of task scheduling. Combined, descriptors and instantiation functions provide a mechanism to concisely represent the structure and communication patterns of tasks of varying granularity while still operating with overhead appropriate to a dynamic framework.

#### 1.1 Motivation

#### 1.1.1 The Manycore Era

Trends in microprocessor design and production point to a new era where processors have increasing numbers of cores rather than improved single-core designs. This trend has been prompted by the ever-increasing transistor budgets available for additional logic and the matching challenges to fully profit from it. Practical limits have been reached for clock speeds and exploitable instruction-level parallelism. Signal propagation time around the die creates timing limitations. The density of transistors increases the power use and heat dissipation required. CMPs offer the possibility of significantly improving performance potential, as long as the software can adapt to this new era.

Indeed, software presents the greatest challenge of the manycore era: how to fulfill user expectations for performance improvements while managing the variety of architectures and environments that are sure to exist. We already see great variations in current consumer architectures, from low-speed single-core computers to highperformance servers with 32 processing cores immediately available to a program, with various core designs. Current x86 processors are being shipped with support for up to 8 threads per die, and the SPARC T2 can handle up to 64 threads on a single chip. Eventually industry may even produce CMPs with hundreds (some would speculate thousands) of processors.

This variety is sure to increase as the range of cores widens, the design of cores improves, and the possibility of heterogeneity becomes a reality [3]. Every design choice, from the memory hierarchy to the chip layout to the types of processing elements in any particular machine has impacts on parallel performance, and it will be important for programs to adapt to this diversity in order to have full performance. Optimizing for the wrong architecture will either under-utilize the available resources or over-estimate the machine's capabilities.

Architectural diversity is not the only variable that can affect parallel program optimization. In fact, any number of environmental factors, even on the same machine but between separate executions of the same program, may also affect performance. For example, desktop computers see a variety of applications attempting to run concurrently, each with different requirements and capabilities for parallel execution. The program itself may present run-time dependencies that affect parallelism, such as an input data set which places constraints on parallel work and communication. Thus, the resources that may be available to a program may vary between executions or even change on the fly. An application must adapt to these constantly changing conditions.

In many cases, proper parallelization is dependent on the data used by the program, creating computation patterns that cannot be determined until run time. The difficulty for a parallelizing system is to account for the many different situations and environments: it may be possible to optimize for a couple specific situations, but the general case is another matter. All of these factors contribute to the difficulty of effectively parallelizing the program, the main consequence of failure being reduced performance in the final executable.

#### 1.1.2 Discovery of Parallelism

The most difficult problem for parallelizing compilers – and, for that matter, programmers – is finding the parallelism inherent in an application. Parallelizing compilers are an active area of research, and there have been many research compilers working on discovering parallelism in a program, e.g. [4, 5, 6, 7]. Parallelizing compilers have better success with data-parallel programs and coarse-grain parallelism through inter-procedural analysis than with other types of parallelism.

Parallelism is a property of the code and data of a program. Code regions might execute on different sections of data and therefore run in parallel. The same code may execute on separate data regions for data-parallel and loop-parallel programs. Separate code regions working on potentially the same data form task-parallel programs. The compiler attempts to prove that code or data can be parallelized and transforms the program appropriately. An important observation is that parallelism is not a property of the architecture or execution environment.

It is not always possible to discover all parallelism at compile time, which may be dependent on the data set or other run-time factors. The compiler can, however, compute the necessary runtime conditions for code to be parallel. Parallelism can be finalized by the run-time system when the conditions can be resolved.

#### 1.1.3 Packaging of Parallelism

Once the parallel properties of an application have been established, the compiler or run-time system must associate data, loop iterations, or tasks with appropriate threads. The result of association is the *packaging* of the parallelism. Packaging of parallelism is highly dependent on the architecture and operating environment: accounting for these differences is key to extracting the full performance from the execution of a program. The process of packaging consists of mapping and scheduling work to the available resources, organizing and optimizing for the architecture and environment.

Discovery and packaging of parallelism are not orthogonal processes: extracting more parallelism has a direct impact on the packaging/scheduling process, and transforming code to find additional parallelism may alter the dependencies that need to be considered when scheduling. In other cases, the relationship is more direct: for example, each iteration of a Monte Carlo [8] algorithm is easily proved to be independent during the discovery process. The packaging is generally simple, but may be complicated by load balancing.

Even algorithms where discovery is simple may have complications at the packaging stage. In general, the task execution time is not known *a priori* and may vary greatly at run time, creating classic problems with load balance. Dynamic load balancing techniques [9] may help in many situations but may be limited by high overhead, especially for fine-grained parallelism. Static packaging systems must rely

on an estimate of the execution time, an estimate which is assumed to be sufficiently accurate for the application in question.

Task dependencies create both communication problems and load balancing issues: not all schedules of tasks are valid, and different schedules have very different effects on the execution time and load balancing. Communication costs make packaging decisions especially important.

#### 1.1.4 The Run-time Advantage

The discovery of parallelism tends to be an expensive process and must be done at compile time to reduce overhead. However, diversity cannot be managed at compile time. Serial programs have dealt with diversity by deferring some optimization to run time through hardware techniques such as out of order execution. Parallel programs require similar run-time techniques to deal with diversity as run-time dependencies preclude full compile-time analysis. We have proposed [10] a solution similar to the out-of-order technique described above: perform general static optimizations and create a dynamic optimization scheme to account for diversity.

Separating discovery and packaging in the parallelism process allows the high overhead of discovery to be managed offline. The run-time system, freed from this overhead, is free to optimize the parallelism using the wide variety of information available.

#### 1.2 The ADOPAR Vision

The technique of separating the packaging of parallelism from its discovery to overcome manycore diversity is what we call Adaptive Online Parallelization (ADOPAR) [10, 11]. As its name implies, ADOPAR adapts the parallelism of an application to diversity through online (run-time) techniques. The BYU Architecture Research, Design, and Description (BARDD) research group is creating a research infrastructure to implement its principles of diversity-independent discovery and diversity-dependent packaging. BARDD is currently researching the techniques required to create effective packaging. ADOPAR stands in stark contrast to previous methods for parallelizing software. Its process may best be illustrated by examining a program's life cycle.

- 1. Software is developed by a programmer. The focus at this stage is software behavior and description of parallelism, not the packaging or optimization for a particular system. This simplifies the work of a software developer, whose job is to describe the parallelism, not package and optimize it.

- 2. The compiler extracts information about parallelism from the programming model and discovers new implicit parallelism.

- 3. At run time, schedulers present in the run-time system use the results of discovery to package parallelism for best performance in the current operating environment. Generally, this consists of assigning work to processors and accounting for the capabilities and limitations of the available resources. Any program information not available at compile-time (such as the operating data) is also available for packaging optimization.

- 4. The schedule is executed. For some programs, loops and other forms of reuse allow the packaging overhead to be amortized.

- 5. The packagers may need to adapt when conditions change, such as an increase or reduction in the number of threads. Information from profiling may yield better performance through repackaging.

In this process, the ADOPAR infrastructure must interact with the operating system. We envision a process where the run-time system and operating system negotiate for resources. The run-time system requests resources according to its needs while the operating system presents what is available. The traditional process scheduling role of the operating system is transferred to the run-time system so it can manage its own threads (as in [12] and [13]).

By splitting the discovery and packaging phases, ADOPAR achieves the full benefits of parallelism discovery and run-time information. But to use run-time information, the ADOPAR infrastructure requires a dynamic compilation environment. Using a Just-In-Time compiler (JIT) framework offers the opportunity to optimize the code given the task schedule, the specific execution environment, and the runtime data dependencies. Having an on-the-fly compiler also allows for the scheduler to directly work with code primitives such as basic blocks, loops, and functions, as well as run various code analyses as part of the scheduling process. This work uses the Low Level Virtual Machine (LLVM) [14] infrastructure, a compiler framework that includes the ability to add analyses and transformations, create new compiler intrinsics, and optimize and generate machine code for several instruction set architectures at runtime.

#### **1.3** Parallelism Representation

One key element in ADOPAR is a mechanism to communicate the results of discovery to packagers. Since discovery occurs at compile time and packaging occurs at run time, a persistent representation of parallelism is needed. This work describes a representation suitable for an ADOPAR infrastructure that can act as a bridge between discovery and packaging. The goal of the framework's representation make sufficiently detailed information available to the packagers and present it conveniently. More detailed information allows the scheduler to provide a more efficient mapping of tasks to processors; a convenient format reduces the analysis overhead of the program while compiling, scheduling, and executing. ADOPAR requires the following from its parallelism representation:

1. Irregularity

ADOPAR's specific goal is to parallelize programs with irregular features; the representation needs the ability to conveniently express many types of irregularity. Some applications are completely irregular (random or nearly so) while others may have a complex pattern. The representation must handle either case conveniently and compactly.

#### 2. Regularity

While ADOPAR attempts to optimize irregular applications, some programs have a mixture of regular and irregular properties. A representation that can handle irregular applications (possibly by enumerating each task) will be able to work with regular applications as well, although the memory usage and processing time may not be optimal. Instead, a direct means of representing regularity in a program may reduce processing time significantly.

3. Communication

Almost every parallel application requires communication between processors during the computation. Often, the communication time constitutes a significant portion of the total execution time. One of ADOPAR's goals is to consider the communication costs and optimize the scheduling appropriately. The representation should effectively represent communication regardless of whether the application is regular or irregular.

4. Low Run-time Overhead

ADOPAR may be used with fine-grained task models, which leads to increased interaction with the representation. Lowering the overhead of the representation is critical when dealing with many tasks.

We refer to the parallelism representation as an Internal Representation (IR), in analogy to the internal representations used by compiler frameworks, since the representation is internal to the infrastructure, communicating between its separate components. The IR presented in this work will be evaluated according to the requirements of ADOPAR.

#### **1.4** Contributions and Objectives

This work contributes a new way of viewing internal representations for parallelism. While previous methods have been constrained by the programming model or arbitrary schemes, this new representation is very flexible and expressive. This representation forms the connective infrastructure to bridge the gap between the static discovery and the dynamic packaging that comprise the ADOPAR infrastructure. The exposed interface allows for a variety of programming models to integrate with the system while still using their native format within ADOPAR IR.

The following mechanisms comprise the IR:

- **Task Descriptors** Similar tasks are bundled together and represented as a single task descriptor. Using descriptors potentially simplifies static analysis of parallelism and can represent both regular and irregular computations. On the surface, task descriptors act as task "factories", but might be more accurately viewed as a description of a group of tasks.

- **Relationship Descriptors** Because tasks are condensed in the representation, the relationships between them must also be represented in a similar manner. Both regular and irregular relationships may be represented.

- Instantiation Functions The key contribution that makes task and relationship descriptors possible is an algorithmic representation of parallelism and relationships as a method of the descriptors. In other words, instead of specifying task parameters directly, the front end provides the computation to specify these parameters. In the case of constant parameters, there is little difference; however, irregular and complex properties may be expressed algorithmically. Having the capability to express complex patterns algorithmically is especially important for irregular computations: the computations may have a pattern that may not be possible to define with any one regular system, but an arbitrary sequence of code may describe it. Instantiation functions may be analyzed to find regular patterns at compile time or executed at run time to instantiate the tasks themselves.

This IR presents flexible and descriptive information about parallelism to an ADOPAR infrastructure. Instantiation functions allow flexibility that stands in stark contrast with the strict constraints used by other representations. Overall, the representation adds a significant amount of additional parallelism information while increasing the code size by less than 20% for even fine-grained parallelism and negligible additional compilation time. We will show that while it is possible to produce a traditional task graph for schedulers to use, it will be important that schedulers operate on the native representation to minimize overhead.

#### 1.5 Outline

The rest of this work is organized as follows:

Chapter 2 presents related work in the area of parallelism representations and other background information. Various compilers and run-time environments for parallel systems use an internal representation appropriate for the techniques used by the same. These representations are compared to the requirements of ADOPAR.

Chapter 3 describes ADOPAR's representation. The description includes several examples of task graphs that a front end might create. Also, various optimizations and operations that may be performed on that task graph are discussed.

Chapter 4 details the implementation of the representation, along with continuations of the examples in Chapter 3. This chapter also describes the programming API and the back-end programming model of the ADOPAR IR.

Chapter 5 evaluates the representation by the overhead that it incurs while building and operating on the task graph. It also shows how well this new representation integrates with various front ends.

Finally, Chapter 6 presents future work that can be performed in this area of research and some final thoughts on this thesis.

## Chapter 2

### **Background and Related Work**

The proliferation of multicore processors has stimulated continuing and extensive research in optimizing compilers and other methods of increasing parallelism. Much of this research has required development of a method to express parallelism. In some cases, parallelism is presented as part of the programming paradigm; in others it is defined as the compiler's or tool's internal representation for the parallelism.

This chapter summarizes the various paradigms that have been developed and the internal representations used and presented in literature. The remainder of this chapter is organized as follows: first, scheduling and execution is examined in context of parallel programming. Next, an overview of relevant programming paradigms is presented, followed by a discussion on how data-parallel, loop-parallel, and taskparallel programs are represented in other systems.

#### 2.1 Scheduling and Execution

There are several methods for scheduling and executing the parallelism of a program. *Static scheduling* is the process of taking tasks, loop iterations, or data (depending on the type of parallelism) and assigning them to a processing element all at once. While generally performed at compile time, static scheduling may also be a single step before execution, introducing a one-time execution overhead. Static scheduling is especially effective for regular programs but can be inefficient if the parallelism has a dynamic or irregular nature.

Other applications simply cannot be scheduled statically. For example, some irregular applications delay task creation until after other tasks have been executed. When tasks are created dynamically, a common solution is to have a "bin" of ready

tasks, from which work is assigned to available processors. *Dynamic scheduling* is a mechanism which operates on the collection of tasks and makes task assignments during the execution of a program. Dynamic and irregular programs tend to match the paradigm of dynamic scheduling (where static scheduling would be inappropriate or inefficient), but the run-time assignments introduce critical execution overhead that must be avoided as much as possible.

A compromise for those cases where static scheduling may be appropriate if the dynamic nature can be resolved is to schedule at run time but before the actual execution. Being a form of static scheduling, it involves examining the parallelism first and then making assignments. The Inspector-Executor (IE) model, first proposed by Saltz [15], has been proposed as a method of dealing with irregular communication and data layout in many applications, but has found support in many other research areas as well. The CHAOS/PARTI compiler framework [5] contains an implementation of the IE model.

The core concept is to separate execution into two phases: an *inspector* and an *executor*. The inspector preprocesses the data to determine the necessary communication pattern, passing this information on to an executor which does the actual computations. The preprocessing may also consist of optimizing the execution order for cache effects, etc. Separating the inspection of the loops from the execution gives opportunities for scheduling and optimization. Any overhead incurred may be mitigated by repeatedly reusing the results of the inspector phase.

IE has been used for sparse linear algebra. Sparse matrix execution and other similar computational problems are a case where the indexes to an array may be expressed as functions (e.g. a[f()] = g(b[h()])). The basic task is defined by a loop (or loop nest) that operates on the matrix, but the number of tasks and their dependencies are not known until the indexes are calculated. Thus, the IE model breaks execution into two phases: an inspector that calculates the loop indexes and then an executor that then uses those indexes. The model usually operates as a loop, the iterations of which are scheduled to threads in a simple fashion. Although reusing the results of the inspection phase is helpful in amortizing overhead costs, it is still important to reduce overhead as much as possible. To that end, the original IE model uses a simple *wavefront* scheduling process, a scheme similar to As Soon As Possible (ASAP) schedulers. In wavefront scheduling, the tasks to schedule are represented as a Directed Acyclic Graph (DAG). All nodes without predecessors are scheduled in parallel as the first wavefront. These nodes are removed from the graph and the new set of nodes without predecessors is scheduled in parallel as the second wavefront. This procedure continues until all nodes are scheduled. Computing the wavefronts is a low-overhead task for the run-time environment. Creating this schedule is simple and may itself be parallelized with low overhead; however, the schedule produced is not optimal, especially for fine-grained tasks.

IE can be used for more than just parallel programming: the same concept can be applied to serial programming where data access needs to be analyzed. The result of the inspector is a sequence of memory references that could then be reorganized to maximize cache efficiency. The abstract concept of inspecting the data access patterns (as a preprocessing step) and determining a work schedule is a generic concept that may be applied in many situations. Many of the programming representations presented in the following sections use the IE concept by providing a mechanism for partitioning parallelism and then reusing this partitioning repeatedly during the actual execution. This is also the paradigm used by ADOPAR; this work presents the communication mechanism between ADOPAR's inspector and executor concepts.

### 2.2 Parallel Programming Paradigms

There are many paradigms for programming parallel systems, with more being developed constantly. Each attempts to simplify the specification of parallelism, increase the amount of parallel work, decrease overhead, or optimize for specific hardware. These paradigms may be expressed as language constructs, library calls, or compiler directives, often placed on the top of traditional, serial languages.

Some newer programming languages have the built-in ability to perform parallel operations. Single-assignment languages, functional languages, and process-based languages all fall under this category. Traditional languages, however, form the mainstay of benchmarks and legacy code. Many developers would prefer to parallelize existing code or at least use a language with similar constructs. For this reason, High Performance FORTRAN (HPF), FORTRAN 95, and others were made as extensions of FORTRAN. C and C++ (as well as FORTRAN) have been extended with OpenMP and various libraries to transform them into parallel languages.

For the purposes of this work, we define *parallelism* as the properties of program segments that allow them to run concurrently. Shared data between program segments limit, prevent, or otherwise constrain parallel execution.

#### 2.2.1 Types of Parallelism

Most parallel programming paradigms fall into the following categories:

- **Data-Parallel** (Section 2.3) This type of parallelism is defined by the data being operated on. In general, a thread "owns" a portion of the data and operates on it. Irregular data divisions create imbalance in the load balance and communication in the system. Parallelism is intrinsically defined by the data division.

- Loop-Parallel (Section 2.4) For many applications, loop iterations can be independently executed in parallel. A compiler may have to transform the loop and prove independence to parallelize programs. Loop-parallel programs may be irregular if the amount of work in each iteration varies or if not all loop indexes should be performed. Parallelism is defined by the division of loop iterations.

- **Task-Parallel** (Section 2.5) A third class of parallel programs are defined by tasks: portions of the program that may be executed simultaneously and, depending on the model, atomically. There are generally more tasks than threads or processors in a system: tasks must be scheduled or mapped to a thread or processor at the appropriate times while not violating dependencies. Scheduling often involves some sort of *task graph* or similar representation. Task graphs show irregular tasks and communication directly, and can usually represent an equivalent form of both the data-parallel and loop-parallel paradigms by defining

loop iterations and portions of the data to be the individual tasks. Parallelism is defined by the task graph.

### 2.3 Data-Parallel Representations

Data-parallel programming recognizes that the same set of operations may be applied to a block of data. The block can then be divided between processors for parallel operation. Data-parallel programs may be specified by:

- 1. control-flow of operations on a data set,

- 2. partitioning of the data to processors, and

- 3. communication and synchronization.

Kernel Lattice Parallelism (KeLP) [16, 17] is a set of C++ libraries designed to ease the specification of irregular block-wise data layouts, where sections of matrices are segmented into individual blocks to be assigned to different processors. Blocks are partitioned among processors through geometric operations. Communication is specified as sequences of data motion between these blocks. The motion may be set up and then reused throughout execution of the program. A simple example of KeLP is a simple dimension-wise decomposition of the data into rectangular sections. Each block then receives "ghost cells" around the border, representing the communicated data between processors. The data motion for each iteration of the program copies the data in these cells between processors.

KeLP succeeds in representing regular applications and some irregular applications, although irregularity must be described in blocks. Some very irregular programs see a high overhead from the block-wise decomposition. In addition, KeLP is a strictly runtime-only environment, eliminating compile-time analysis of the representation.

The ParaScope compiler tool suite has a special representation for interprocedural side-effect analysis using Regular Section Descriptors (RSDs) [6]. Largegranularity parallelism can only be found by determining that code sections are independent of others, especially code that operates on an array. The compiler may separate code sections for execution if the compiler can prove that different code blocks or iterations of a loop operate on independent sections of an array. ParaScope works on FORTRAN input and creates parallelism by transforming sequential DO loops into parallel DO loops.

ParaScope approaches proving independence through regular sections: an analysis of the access patterns across an array. A *regular section* is a commonly used access pattern over a portion (*section*) of an array, such as a column or row. A regular section defines a set of actual data accesses, including the operation performed that data. Set intersection reveals dependencies between two code blocks; set union combines regular sections. There are many possible ways of representing regular sections: some of these methods will be analyzed below as variations on the RSD. The easiest regular section representation is a vector of indexes. This could contain a single element, row, column, or diagonal. Triangular sections and discontinuities have no representation in RSDs. While irregular patterns may require many RSDs, regular patterns potentially have very low overhead. Working with RSDs is mainly a compile-time process but might also be applied in a run-time system.

As a refinement of the RSD, the Data Access Descriptor (DAD) [18] defines three properties for a task's access to a portion of an n-dimensional array. The main contribution is the *simple section*, a simple boundary around the accessed portion of an array. By limiting the boundaries to  $45^{\circ}$  angles a maximum of  $2n^2$  boundaries are available to describe sections, sufficient for most standard applications. Constant-time operations are also available to define the intersection and union of simple sections, with the complication that the union may not result in a completely convex region. As a solution, the conservative approach expands the region so it satisfies simple boundary conditions. In addition, a *traversal order* and *reference template* (the definitions for how the code accesses descriptors) are provided for each DAD as it is defined for an array. DADs have many of the same benefits and drawbacks as RSDs, but also have the ability to describe other shapes of regular sections and attach additional access patterns for communication. Processor Tagged Descriptors (PTDs) [19] further extend the RSD and the DAD. The bounded area is more precisely defined, allowing for concave sections and other complex shapes, while requiring more processing to perform arithmetic on these sections. Instead of bounding an area by known lines, the boundaries are parameterized by the processor number and a linear equation. These restrictions still allow for simple mathematical operations to manipulate the descriptors. The parameterizations automatically partition the data among processors, the number of which may vary from run to run with the same binary and descriptors. As with RSDs and DADs, PTDs are mainly used for analysis by the compiler, rather than an inherent descriptor of the parallelization. However, the results may be used later as the descriptors reveal the end data partitioning. Of the three descriptors (RSD, DAD, and PTD), the last has the greatest flexibility for describing irregular accesses.

A different approach is used in Pilar's internal representation, Communication Pattern Internal Representation (CPIR) [20, 21]. Many applications show a mixture of regular and irregular communication patterns. Three basic constructions are used by the Pilar compiler to represent data access patterns: *intervals*, *enumerations* and *cyclics.* Intervals are similar to the descriptors previously described: a set of bounds on the index ranges for data access. CPIR intervals are actually a collection of such ranges. Enumerations allow for completely irregular access patterns and are a simple list of all individual accesses. Cyclics provide a specific access pattern: for some applications, access is regular but an interval is not sufficient. Instead, the list may be strided like the diagonals of a matrix. Such a list may be inefficiently represented as an enumerated list, but cyclics allow for a smaller memory footprint and faster set operations. An access schedule (meaning, the ordering of element access within the construct) is also created in addition to the data pattern. This schedule is then used to better analyze the relationships between different patterns. Since CPIR is a messagepassing system, the schedule consists of the sequence of messages to communicate CPIR primitives, which are then translated to the actual local addresses.

Pilar has the ability to describe very regular and irregular systems (a feature important to ADOPAR) and some capability to describe simple patterns when necessary. The pattern is limited to simple, strided array accesses, which results in lower overhead for those applications that it describes well.

These various versions of regular sections are a useful concept for ADOPAR, but are constrained to specific formats for these sections. They are also constrained to array accesses, a limitation that ADOPAR must avoid. The ability to describe various patterns, however, is a concept that is useful in a more advanced parallelism representation.

#### 2.4 Loop-Parallel Representations

Most automatic parallelizing compilers attempt to find coarse-grained loop parallelism. Loop parallelism is easy to express: simply mark loops as being parallel and map individual loop iterations to threads. Representations for loop-parallel programs generally have attributes such as:

- 1. special parallel loops (such as DOALL or DOACROSS),

- 2. mapping of iterations to processors, and

- 3. communication and synchronization.

The Polaris compiler's Internal Representation (IR) [7] has a 1-1 relationship with basic FORTRAN constructs using a high-level format. Expressions, statements, and symbol tables are basic classes. Parallel loops, after appropriate analysis, become doall loops, where each iteration may be executed in parallel. Variables may be declared as private to the loop.

Polaris is similar to the OpenMP [22] standard. OpenMP is a set of compiler directives for C and FORTRAN programs, including automatic partitioning of loops and parallel sections to processors, synchronization through barriers, etc. The parallelism described by OpenMP is implicit, specifying which variables are private and which loops may be executed in parallel. Some hints as to scheduling may also be specified, but such control is limited.

In both cases, irregular applications are not well-supported: iterations that do nothing are generally assigned to processors along with those that perform useful work. Loop-based representations have few facilities to express communication and dependencies beyond the use of barriers and other simple primitives. These representations are often translated to a simple back end where loop iterations are simply divided between processing elements, reducing the optimizations possible at the back end.

The Stanford University Intermediate Format (SUIF) compiler [4, 23] is an extensive project to increase the ability of compilers to automatically extract parallelism from existing benchmarks. Internally, programs are represented on a relatively high level: loops, conditional statements, and array accesses (as well as other helpful information from the front end) are part of the IR, as well as the more common low-level information used by a compiler. High-level information is in a canonical form for the compiler passes to use. After the high-level passes have completed, the high-level information is transformed into lower-level compare/branch instructions, etc.

The higher-level IR of SUIF allows for easy analysis, but is not strictly meant for use by a unifying back end such as ADOPAR. Higher-level information is useful (as little information is lost when lowering to machine instructions), but needs to be in a form that can be scheduled and executed. In the end, SUIF has many of the same limitations as other loop-parallel representations, which are all limited by the implicit nature of loop parallelism.

#### 2.5 Task-Parallel Representations

Task graphs are another way to represent parallelism. Individual units of work (tasks) are separated and reconnected by their dependencies and ordering constraints. The sequence of dependencies determine which tasks may be executed simultaneously; therefore, the dependencies are critical to determining ordering, scheduling, and partitioning. Analyzing each dependency reveals the constraints to the available parallel work. The requirements for task-parallel representations are different than those for other types of parallelism. Task-parallel representations require:

- 1. code and data for task execution,

- 2. task dependencies, and

- 3. additional synchronization between tasks.

Johnson proposed a task graph specially designed for dynamic task scheduling [24]. This task graph assigns specific states to each task: unexecuted, executing, finished, and not ready. As tasks become available they are processed by threads. A task structure handles dynamic creation and execution of tasks. Tasks are never explicitly scheduled to reduce overhead or increase locality as some applications have unpredictable and non-repetitive behavior. Use of this task graph requires good heuristics appropriate to the problem in order to properly and efficiently execute tasks.

The nature of this task graph makes both regular and irregular applications easy to represent. Communication and dependencies are represented as well as part of the task graph. The execution overhead, however, may be too large for fine-grained applications: tasks are dynamically assigned, so the overhead is not amortized by reusing information. In addition, little or no static analysis is possible.

The Hierarchical Task Graph (HTG) [25] was made as part of the autoscheduling project headed by Polychronopoulos [26]. As its name implies, the HTG describes a task graph in a hierarchical manner: loops in the control-flow graph are collapsed into a single node (similar to a strongly-connected component). These nodes may be further collapsed to change the granularity of the task graph. The edges in the graph represent the communication and dependencies between tasks. The overall preconditions necessary to execute a task are represented by a set of *execution tags*. Redundant tags may be optimized for run-time efficiency.

The HTG satisfies many of ADOPAR's requirements: it may express irregular applications and communication with minimal task overhead. Indeed, this thesis borrows several techniques from the HTG and may be considered an extension of it in many ways: the basic task graph and the hierarchical structure being key examples. However, the HTG makes no provisions for regularity as its focus is on dynamic, rather than static, scheduling. ADOPAR, however, requires a more flexible representation for the scheduler to work with and using the HTG with many fine-grained tasks will exaggerate overhead issues; some method of condensing and summarizing tasks is a step to mitigate this problem.

## 2.6 Summary

Various representations exist to represent parallelism, each with its own implementation infrastructure. Many representations follow the general idea of the IE model: perform some sort of analysis before running the program in some reusable fashion. The needs of the infrastructure tend to determine the properties of its respective representation. For example, the need to analyze dependencies specifies a data-based representation with set operations, while iterating algorithms call for a loop-based representation. Dynamic and irregular problems may require a task-based representation.

ADOPAR's representation has specific requirements: the representation must handle irregular and regular tasks and communication patterns in both compile-time and run-time environments, all with low overhead. Many of the representations used in other parallelizing environments have been presented here, but none completely fulfills the requirements of ADOPAR, especially the requirement that a representation can cross the boundary between a compile-time environment and a run-time environment.

The following chapter describes a new IR for ADOPAR. The IR uses a task graph described in the program's code with compiler intrinsics. The IR handles irregularity and regularity using executable code as part of the representation itself, making a very flexible system within a compact representation that may be analyzed within the compiler or run-time system.

23

# Chapter 3

# The ADOPAR Representation

ADOPAR is an execution framework designed to improve parallel performance by overcoming environmental and architectural diversity and by increasing the efficiency of parallelization. ADOPAR has a special focus on applications with irregular communication and data access patterns. To this end, ADOPAR uses the following concepts:

• Fine-Grained Task Model

Task parallelism is a flexible method to express both regular and irregular parallelism, but most research has been limited to coarse-grained tasks. Large tasks generally have the advantage of fewer inter-task dependencies, simplifying scheduling and reducing overhead. As the task granularity becomes more fine, however, more parallelism may be extracted from the program. The additional parallelism, in turn, increases potential for a better-balanced load and tighter overall schedule. ADOPAR attempts to mitigate the overhead while still extracting sufficient parallelism to justify the extra work of scheduling.

• Front-End Agnostic

ADOPAR does not rely on any one specific programming paradigm in the front end but may be used as an optimizing back end to many different languages and systems. Any model that can be represented as a set of tasks (which include most data and loop parallel systems) may then use ADOPAR for an optimization and execution environment. No front-end yet exists that produces the ADOPAR Internal Representation (IR), a problem outside the scope of this work. • Dynamic Execution Environment

Dynamic code compilation offers many advantages for any system trying to overcome diversity challenges (like the architecture differences and environment changes described in Chapter 1). Run-time compilation may take the architecture diversity into account automatically; changes in the number of available processors or additional overhead in the communication on the system imply that portions of the program may even need recompilation for optimal performance.

• Run-time Optimization System

The ability to compile code dynamically allows for run-time optimizations. Dynamic optimization is especially important with irregular applications, but also can be effective for serial applications as well [27]. In addition, hardware and operating systems provide performance counters – useful for refining the compilation and schedule of a parallel system. Lastly, run-time optimization can potentially reduce the run-time overhead of fine-grained tasks significantly by intelligently merging the tasks together.

ADOPAR requires an internal representation in order to take advantage of each of these concepts. This representation must include the dependencies between each task and the synchronization necessary to execute correctly. In addition, the representation needs to be as compact as possible while still providing rapid querying for scheduling and analysis.

Note that this representation is significantly different from many of those described in Chapter 2. Rather than being used as a compiler analysis technique, storing the data access patterns for the various function calls, the ADOPAR representation is a way of integrating a scheduling and executing back end with arbitrary front-end analyses to define a set of executable tasks. Integration is accomplished by including code as a part of the representation, as will be described in Section 3.2. The ADOPAR IR makes a bridge between the static discovery representations and the run-time packaging systems.

### 3.1 Fine-Grained Task Model

The goal of all parallelizing compilers is to increase the amount of parallelism, balance the load between processors, and reduce the amount of communication. Ideally, this goal will be accomplished with as little overhead as possible. Diversity in operating environments complicates each goal. ADOPAR's solution is to separate the process of parallelization into three phases:

- **Discovery** Analyze the program for possible parallelism. ADOPAR allows the use of very fine-grained tasks to maximize the parallelism available in the program. Discovery might be done at compile time or at run time, but compile-time analysis would reduce execution overhead. Discovery is partly the function of a front end, but can also be done by analysis of the IR.

- **Packaging** Map and schedule tasks to threads. Packaging is a well-studied problem (see [28, 29, 30, 31]) but is still an active area of research. Packaging would ideally be done at compile time to reduce overhead, but irregular problems may not be scheduled until the task structure has been resolved at run time.

- **Execution** Perform the scheduled tasks in the specified order. Execution must, of course, be done at run time, and may be augmented by performance monitoring for schedule tuning.

Notice that these phases are very similar to the Inspector-Executor (IE) model: the discovery phase inspects the program for parallelism and the execution phase performs the parallel calculations. An intermediate phase (packaging and scheduling) optimizes the parallelism and reduces communication. Fine-grained tasks, while allowing for additional parallelism, introduce more communication and overhead; the scheduling phase offers a chance to reduce overhead. IE is limited by a very simplistic packaging algorithm (wavefront scheduling) and has only limited static capabilities.

The extra overhead of fine-grained tasks requires that compile-time analysis must be done when possible. Irregular communication patterns will usually prevent scheduling at compile time, but discovery may still be done. Thus a mechanism must exist to transfer the parallelism between the static environment and the dynamic environment.

#### 3.2 Static Task Graph

The main feature of the ADOPAR IR is a *task graph*, similar to those described in Chapter 2. A task graph offers a simple, well-studied representation and is the underlying data structure used by the ADOPAR scheduling system. A goal of the IR is to work with a variety of programming paradigms; task graphs offer a universal mechanism to represent many types of parallelism.

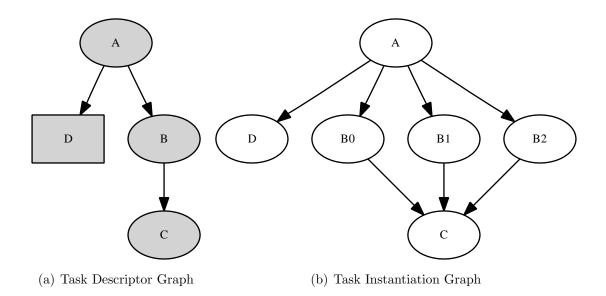

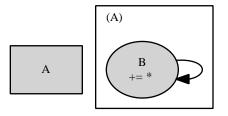

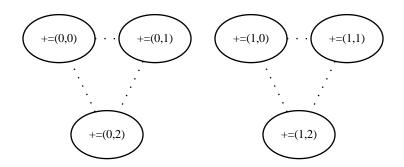

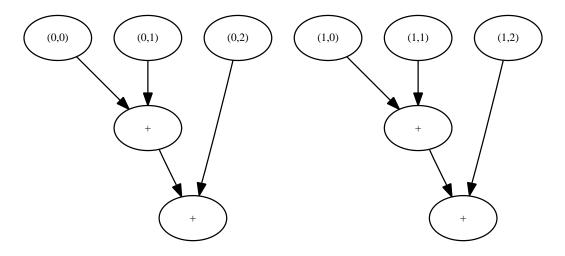

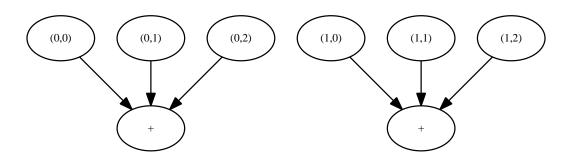

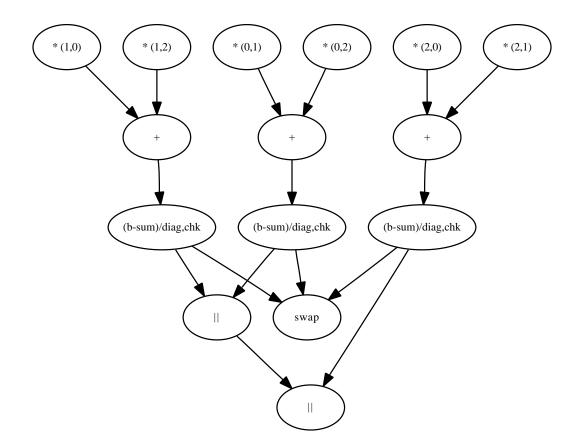

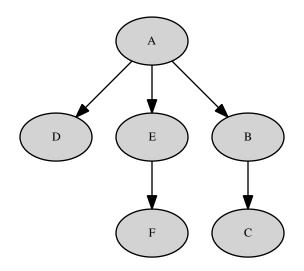

The underlying data structure is similar to the Hierarchical Task Graph (HTG) but with the addition of highly generic *task descriptors* and *relationship descriptors*: nodes and edges in the task graph that represent an unspecified number of tasks, subtasks, and relationships. Nodes often take the place of loop iterations, where each iteration may be considered a task. Using these nodes, a front end may represent a large number of similar tasks in a very compact form. Figure 3.1 demonstrates how this works in a trivial graph. The program defines a set of task descriptors (a), where node B in fact represents a set of nodes. At run time, node B is instantiated to create nodes B0, B1, and B2 (b). The instantiated nodes may be actually created or just implied in the implementation. As will be seen in Chapter 4, it may be more efficient to do one or the other, depending on the task graph structure and how the instantiation is specified.

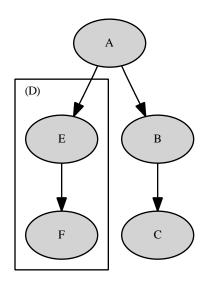

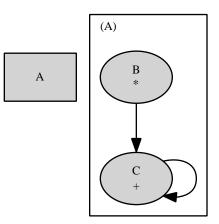

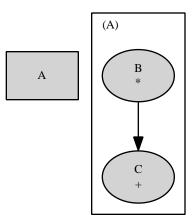

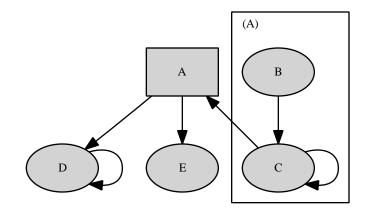

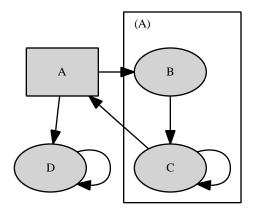

In addition to representing sets of instantiated tasks, task descriptors may be a hierarchy of other task descriptors, similar to the hierarchy mechanism in the HTG. A hierarchy is the grouping of task descriptors rather than of individual tasks and serves a different purpose. Rather than containing loops, the hierarchy consists of additional task descriptors, as seen in Figure 3.2. Of course, the hierarchy is not strictly necessary as the inheritance of dependencies could be carried out manually. A hierarchy provides the framework for a set of transformations to convert the representation between these different forms: more will be given on these operations in Section 3.5.

Figure 3.1: A visualization of the tasks made by the task descriptors. Node B is a task descriptor for three instantiated tasks. (a) shows the static TDG, (b) shows the instantiated task graph represented by (a).

Figure 3.2: Example of a hierarchy of tasks. Nodes represent task descriptors, with sequencing and conflict relationships represented by the edges in the graph. Nodes E and F form a hierarchy within node D.

The basis of the representation is a graph of task descriptors, which we designate as the Task Descriptor Graph (TDG). The task descriptors may form loops or may be hierarchical. The scheduling back end for ADOPAR, however, operates on a simple Directed Acyclic Graph (DAG) of individual (*instantiated*) tasks, called the Task Instantiation Graph (TIG). The TIG no longer contains this hierarchy and cannot contain loops (which have no meaning to the scheduler). The TDG may be converted to an TIG by instantiating out each task and relationship represented by the descriptors.

The figures in this work distinguish between TDGs and TIGs by shading the nodes of task descriptors. Because the IR is based on a graph, most of the figures will use standard graph notation consisting of nodes (ovals) and edges (lines and arrows). The nodes of the graphs represent the tasks while edges represent the relationships between them. Relationships may be directed (arrows) or undirected (dotted lines). Directed edges are used for sequencing relationships while undirected edges are more appropriate for mutually exclusive and read sharing relationships where no direction is implied by the relationship itself. Hierarchical nodes (only in TDGs) are represented by including a sub-graph of the contained tasks within a separate box annotated with the parent node's name. The parent's node is a rectangle instead of an oval to reflect this hierarchy.

## 3.2.1 Task Types

To support the front-end programming model, the IR includes several task types. Some task types are vital to the functioning of the TDG while others are for convenience. The types of tasks may be expanded in the future; the currently supported tasks are:

- Root Task The root of the task structure. It contains no body (like an empty task) and cannot be contained within another task (but see also Substitution Task below).

- **Empty Task** A task which has no body: its only purpose is to be a hierarchical placeholder for task descriptors.

- **Block Task** A set of basic blocks for the task body, where the control flow through the blocks has a single entry and exit point; loops and branches may exist between these two points.

- **Function Call Task** A single function call, with subtasks defined within the function call itself.

- **Substitution Task** A mechanism for creating dynamic task structures (an entire task structure may be substituted in its place).

#### 3.2.2 Synchronization Primitives

The ADOPAR representation does not have any specific synchronization primitives beyond those implied by task relationships. The scheduler is required to insert the appropriate synchronization between tasks to enforce serial or exclusive execution where it is required. Of course, synchronization need not occur when two tasks have been scheduled in the appropriate order on the same processor. The duty of a front end is to describe relationships: synchronization is then a property extracted from those relationships.

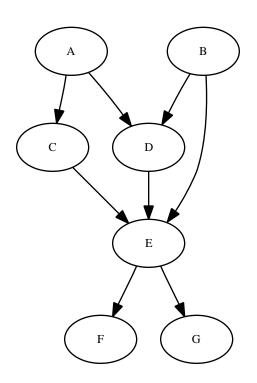

The relationships between tasks determine how they must be scheduled: dependencies on shared variables may force two tasks to become serialized (task dependencies) or simply prevent them from executing simultaneously (mutually exclusive tasks). Relationships are described as edges on the graph. Serial relationships in the graph are enforced at run time through binary semaphores; the latter of the related tasks does not execute until the earlier task signals its completion. A semaphore is signaled once the task ordering is satisfied. Synchronization is not necessary when ordered tasks are scheduled onto the same thread, but they must be scheduled in the correct order if the schedule is to be correct. Conflict relationships require that tasks cannot execute simultaneously. The execution order of two tasks is not important as long as they are not executed simultaneously on separate processors. In this case, the scheduler must either schedule exclusive tasks to the same thread or to separate threads with appropriate locking synchronization to prevent simultaneous execution. Barriers, where a set of threads must wait until all have reached the same point, exist but not as a specific function call or other primitive; rather, the TIG may be organized so that a barrier is simulated. Figure 3.3 shows an example of such a barrier. By forcing all control flow to go through a single empty task (node E in the figure), all threads must wait on the completion of that task. Partial barriers consist of only a portion of the graph passing through the controlling node. Shaping the graph through a barrier allows the scheduler to control which threads must wait on the barrier task.

Figure 3.3: The implementation of a barrier in the ADOPAR internal representation. All tasks must go through node E, which acts as the barrier.

## 3.3 The ADOPAR Internal Representation

ADOPAR uses schedulers that operate on a well-defined task graph, but tries to not be constrained by any single front-end programming paradigm. The ADOPAR internal representation is formed by two major principles:

- Tasks are defined in the program executable, but not instantiated until run time. Delayed instantiation is accomplished through *task descriptors* and *relationship descriptors*, parameterized task graph primitives defined in the executable.

- 2. Few restrictions should be placed on the tasks to provide compatibility for a wide variety of front ends. ADOPAR runs within a Just-In-Time compiler (JIT) environment, enabling executable code to be part of the representation. *Instantiation functions* of descriptors contain this code and perform the task and relationship instantiation.

### 3.3.1 Task and Relationship Descriptors

Task descriptors are a powerful concept that can represent a class of tasks. However, descriptors need some mechanism for specifying how many tasks are to be created, what the parameters are for each task, and how the tasks relate to each other. Different paradigms force the representation to be very generic, especially within applications that have irregular communication patterns. Previous work has limited the user to a specific constraint system to simplify operations on the sets (such as unions or intersections), with anything that does not fit these constraints defaulting to singleton sets (an enumeration). ADOPAR takes a significantly different approach by allowing instantiation functions of any form.

The instantiation functions are actual code provided by the front end, rather than a predefined form, such as a linear equation, where the user only has control over the constants that control the representation. The ADOPAR IR has the capability of executing instantiation functions in a JIT compiler or at compile time if the necessary parameters are available. In fact, there are normally no calls to the representation functions outside of the representation implementation. In those cases when static analysis is not possible, the representation function is not called until the tasks are actually instantiated and the TIG built during execution.

An instantiation function for a task descriptor has access to the parameters of the instantiated parent task in the task hierarchy. The instantiation function creates a set of subtasks using the task parameters. In addition, the parameters of each subtask are initialized with data specific to the task, such as array indexes to access when executed. The ADOPAR schedulers have the capability to schedule based on a task cost: the instantiation function may provide an estimate of execution cost as part of instantiation. This estimation takes precedence over that provided by the definition of the task descriptor.

Any number of schemes are possible due to the flexibility of instantiation functions. For instance, a task descriptor may represent the contents of a DOALL loop by instantiating a task for each iteration and assigning the loop index as the parameter of each task. Tasks using sparse data may analyze the matrices and determine the specific elements that need to be computed, either creating a task for each item or storing information about the element as a task parameter. Examples will be seen in Section 3.4. Regular access patterns may operate as a special case: analysis of constants and partial evaluation [32] will provide the compiler with enough information to perform static analysis.

Providing instantiation functions supplies the user with immense flexibility in their programming model: any number of front-end representations may be used and then easily integrated into the ADOPAR representation by providing a suitable translation function. In a sense, instantiation functions work as the inspector of the communication and tasks.

Beyond the actual instantiation of tasks, it is also necessary to provide a generic means to represent the relationships between these instantiated tasks. Relationship instantiation is similar to instantiating tasks, but edges in the TIG are created rather than nodes. A relationship instantiation function takes an instantiated task and produces a set of predecessors and successors to that task, as well as the exact relationship and cost associated with any communication involved. The definition of a relationship descriptor also contains an estimate of the communication cost, an estimation for the type of relationship, and even association with a variable (so alias analysis results and other information may be encoded). There are five possible relationships between tasks:

- **Read After Write (RAW)** A "true dependency" the second task will read the results of the first. Ordering must be enforced between these two tasks.

- Write After Read (WAR) An "anti-dependency" the second task writes to a data location read by the first. Renaming the data location for one or the other can break this dependency; otherwise, ordering must still be enforced.

- Write After Write (WAW) An "output dependency" both tasks write to the same data location. As with WAR, renaming the data location can break the dependency.

- **Exclusive** The ordering of the two tasks does not matter, but they cannot occur at the same time.

- **Read Share** The tasks read the same data, but no ordering needs to be enforced between them.

- **None** No relationship exists, meaning that the scheduler has full control over the execution order of the tasks and no edge exists between instantiated tasks in the TIG. This is the default relationship if none is specified.